Human Machine Interface Circuit Board Cloning

Human Machine Interface Circuit Board Cloning

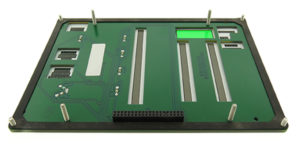

To enable the high switching speed available from the superior FOM, eGaN FETs were developed in advanced land grid array (LGA) packages that not only have low internal inductance, but enable user to design ultra-low inductance into Human Machine Interface Circuit Board Cloning.

To provide the benefits of reduced loop size, magnetic field self-cancellation, consistent inductance independent of board thickness a single sided PCB design, and high efficiency for a multi-layer structure, an improved layout is proposed for eGaN FETs.

Human Machine Interface Circuit Board Cloning

The design utilizes the first inner layer, shown in figure 6b, as a power loop return path. This return path is located directly underneath the top layer’s power loop, figure 6a, allowing for the smallest physical loop size combined with field self-cancellation.

The side view (figure 6c) illustrates the concept of creating a low profile self-cancelling loop in a multilayer PCB. The characteristics of the conventional and proposed optimal designs are compared in table I. The improved layout places the input capacitors in close proximity to the top device, with the positive input voltage terminals located next to the drain connections of the top eGaN FET.

The eGaN FETs are located in the same positions as the lateral and vertical power loop cases. Located between the two eGaN FETs is a series of interleaved switching node and ground vias arranged to match the LGA fingers of the synchronous rectifier eGaN FET.