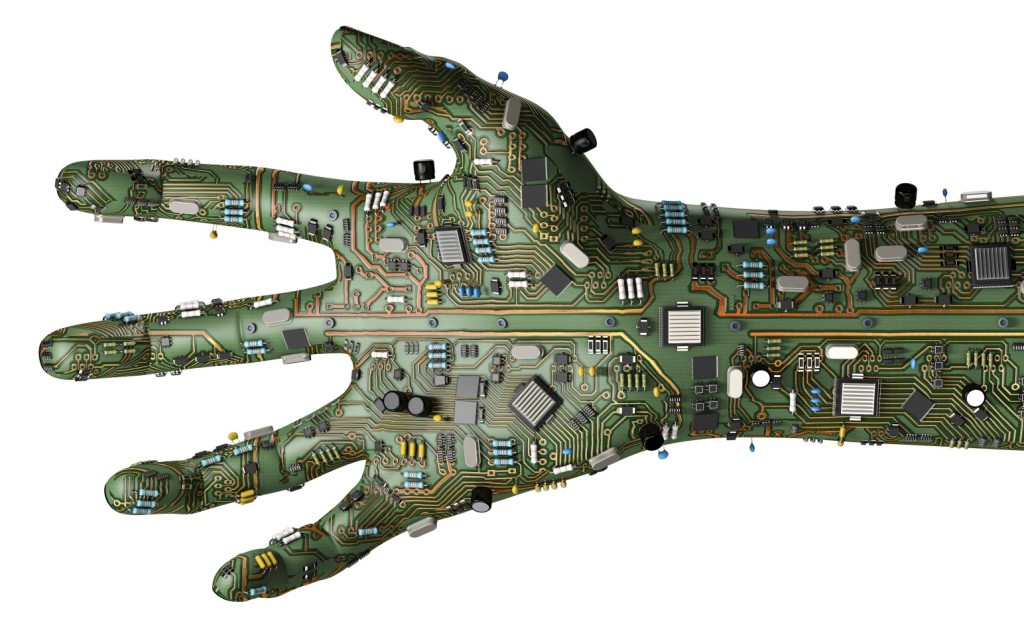

Clone Electronic PCB Board Layout

●Route direction control rules: Clone Electronic PCB Board Layout directions of adjacent layers are in an orthogonal structure, so as to avoid running different signal lines in the same direction on adjacent layers to reduce unnecessary interlayer interference; when it is difficult to avoid this situation due to the limitation of the PCB board structure, especially the signal, When the transmission speed of printed circuit board is high, consider using the ground plane to isolate each wiring layer, and use the ground signal line to isolate each signal line.

●Impedance matching rules: The PCB board layout width of the same network should be kept the same. The variation of the line width will cause uneven characteristic impedance of the line. When the transmission speed is high, reflection will occur, which should be avoided as much as possible in the design. Under certain conditions, such as the lead-out line of the connector, when the lead-out line of the BGA package has a similar structure, the change of the line width may not be avoided, and the effective length of the inconsistent part in the middle should be minimized.

●Line length control rules: The trace length control rule is the short-circuit rule. In the PCB board circuitry drawing copying, the trace length should be kept as short as possible to reduce the interference problem caused by the trace length. Especially for some important signal lines, such as clock lines, be sure to place their oscillators away from each other. The device is very close. For driving multiple devices, the network topology should be decided according to the specific situation.

●Chamfering rules: Sharp and right angles should be avoided in PCB circuit board reverse engineering design, resulting in unnecessary radiation and poor process performance. The angle between all lines should be ≥135°.

●Integrity rules for power and ground layers: For areas with dense via holes, care should be taken to avoid the holes being connected to each other in the hollow area of the power supply and the ground layer, forming a division of the plane layer, thereby destroying the integrity of the plane layer, and thus causing the loop area of the signal line in the ground layer to increase.