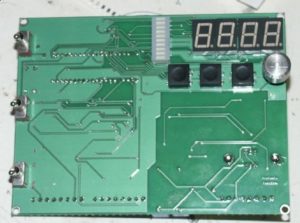

Reverse Engineering Welder Control PC Board Layout

Reverse Engineering Welder Control PC Board Layout

The efficiency results of the three proposed designs from Reverse Engineering Welder Control PC Board Layout compared to a silicon implementation utilizing a vertical power loop with the smallest commercial package, a 3x3mm TSDSON-8, to minimize the power loop. For the Si MOSFET design, the high frequency loop inductance was measured to be around 2 nH, compared to 1 nH for a similar power loop using eGaN FETs.

This is due to the large packaging inductance of the Si MOSFET dominating the loop design. As a result of the superior FOM and packaging of the eGaN FETs, all of the power loop structures outperform the Si MOSFET benchmark design. With the optimal power loop, the efficiency is significantly improved for the eGaN FETs. A 3% full load efficiency improvement is achieved when compared to the Si MOSFET.

For the different eGaN FET designs, the optimal power loop provides a 0.8% and 1% full load efficiency improvement over the vertical and lateral power loops, respectively. For all of the design tests, the optimal layout provides the highest efficiency and lowest device voltage overshoot.

The switching waveforms for the eGaN FET conventional and optimal layouts and Si MOSFET benchmark are shown in figure 10. Both eGaN FET designs offer significant switching speed gains when compared to the Si MOSFET benchmark.

For the eGaN FET with the conventional vertical layout, the high switching speed combined with loop inductance induces a large voltage spike. The optimal layout eGaN FET offers a 500% increase in switching speed with a 40% reduction in voltage overshoot when compared to the 40 V Si MOSFET benchmark. For the eGaN FET with low package parasitic inductance, the layout is critical to switching at high speeds, limiting device overshoot, and improving efficiency.